商机详情 -

浙江AI芯片工艺

芯片的电路设计阶段则更进一步,将逻辑设计转化为具体的电路图,包括晶体管级的电路设计和电路的布局。这一阶段需要考虑电路的性能,如速度、噪声和功耗,同时也要考虑到工艺的可行性。 物理设计是将电路图转化为可以在硅片上制造的物理版图的过程。这包括布局布线、功率和地线的分配、信号完整性和电磁兼容性的考虑。物理设计对芯片的性能和可靠性有着直接的影响。 在设计流程的后阶段,验证和测试是确保设计满足所有规格要求的关键环节。这包括功能验证、时序验证、功耗验证等。设计师们使用各种仿真工具和测试平台来模拟芯片在各种工作条件下的行为,确保设计没有缺陷。利用经过验证的芯片设计模板,可降低设计风险,缩短上市时间,提高市场竞争力。浙江AI芯片工艺

电子设计自动化(EDA)工具是现代芯片设计过程中的基石,它们为设计师提供了强大的自动化设计解决方案。这些工具覆盖了从概念验证到终产品实现的整个设计流程,极大地提高了设计工作的效率和准确性。 在芯片设计的早期阶段,EDA工具提供了电路仿真功能,允许设计师在实际制造之前对电路的行为进行模拟和验证。这种仿真包括直流分析、交流分析、瞬态分析等,确保电路设计在理论上的可行性和稳定性。 逻辑综合是EDA工具的另一个关键功能,它将高级的硬件描述语言代码转换成门级或更低级别的电路实现。这一步骤对于优化电路的性能和面积至关重要,同时也可以为后续的物理设计阶段提供准确的起点。浙江AI芯片工艺降低芯片运行功耗的技术创新,如动态电压频率调整,有助于延长移动设备电池寿命。

除了硬件加密和安全启动,设计师们还采用了多种其他安全措施。例如,安全存储区域可以用来存储密钥、证书和其他敏感数据,这些区域通常具有防篡改的特性。访问控制机制可以限制对关键资源的访问,确保只有授权的用户或进程能够执行特定的操作。 随着技术的发展,新的安全威胁不断出现,设计师们需要不断更新安全策略和机制。例如,为了防止侧信道攻击,设计师们可能会采用频率随机化、功耗屏蔽等技术。为了防止物理攻击,如芯片反向工程,可能需要采用防篡改的封装技术和物理不可克隆函数(PUF)等。 此外,安全性设计还涉及到整个系统的安全性,包括软件、操作系统和应用程序。芯片设计师需要与软件工程师、系统架构师紧密合作,共同构建一个多层次的安全防护体系。 在设计过程中,安全性不应以性能和功耗为代价。设计师们需要在保证安全性的同时,也考虑到芯片的性能和能效。这可能需要采用一些创新的设计方法,如使用同态加密算法来实现数据的隐私保护,同时保持数据处理的效率。

在进行芯片设计时,创新和优化是永恒的主题。设计师需要不断探索新的设计理念和技术,如采用新的晶体管结构、开发新的内存技术、利用新兴的材料等。同时,他们还需要利用的电子设计自动化(EDA)工具来进行设计仿真、验证和优化。 除了技术层面的融合,芯片设计还需要跨学科的团队合作。设计师需要与工艺工程师、测试工程师、产品工程师等紧密合作,共同解决设计过程中的问题。这种跨学科的合作有助于提高设计的质量和效率。 随着技术的发展,芯片设计面临的挑战也在不断增加。设计师需要不断学习新的知识和技能,以适应快速变化的技术环境。同时,他们还需要关注市场趋势和用户需求,以设计出既创新又实用的芯片产品。 总之,芯片设计是一个多学科融合的过程,它要求设计师具备的知识基础和创新能力。通过综合运用电子工程、计算机科学、材料科学等领域的知识,设计师可以实现更高性能、更低功耗的芯片设计,推动整个行业的发展。芯片设计过程中,架构师需要合理规划资源分配,提高整体系统的效能比。

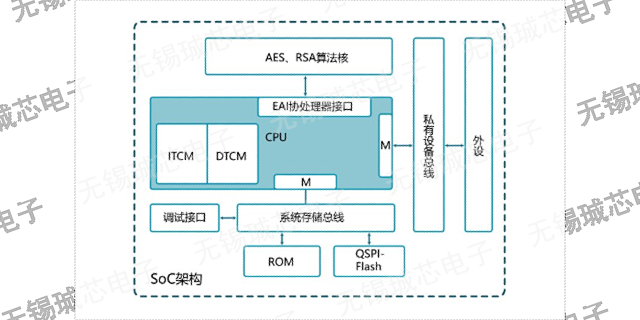

芯片设计的流程是一项精细且系统化的工作,它从规格定义这一基础步骤开始,确立了芯片所需达成的功能和性能目标。这一阶段要求设计团队深入理解市场需求、技术趋势以及潜在用户的期望,从而制定出一套的技术规格说明书。 随后,架构设计阶段接踵而至,这是构建芯片概念框架的关键时期。设计师们需要决定芯片的高层结构,包括处理、存储解决方案、输入/输出端口以及其他关键组件,并规划它们之间的交互方式。架构设计直接影响到芯片的性能和效率,因此需要精心策划和深思熟虑。 逻辑设计阶段紧随其后,这一阶段要求设计师们将架构设计转化为具体的逻辑电路,使用硬件描述语言来描述电路的行为。逻辑设计的成功与否,决定了电路能否按照预期的方式正确执行操作。MCU芯片,即微控制器单元,集成了CPU、存储器和多种外设接口,广泛应用于嵌入式系统。浙江AI芯片工艺

IC芯片,即集成电路芯片,集成大量微型电子元件,大幅提升了电子设备的性能和集成度。浙江AI芯片工艺

可测试性是确保芯片设计成功并满足质量和性能标准的关键环节。在芯片设计的早期阶段,设计师就必须将可测试性纳入考虑,以确保后续的测试工作能够高效、准确地执行。这涉及到在设计中嵌入特定的结构和接口,从而简化测试过程,提高测试的覆盖率和准确性。 首先,设计师通过引入扫描链技术,将芯片内部的触发器连接起来,形成可以进行系统级控制和观察的路径。这样,测试人员可以更容易地访问和控制芯片内部的状态,从而对芯片的功能和性能进行验证。 其次,边界扫描技术也是提高可测试性的重要手段。通过在芯片的输入/输出端口周围设计边界扫描寄存器,可以对这些端口进行隔离和测试,而不需要对整个系统进行测试,这简化了测试流程。 此外,内建自测试(BIST)技术允许芯片在运行时自行生成测试向量并进行测试,这样可以在不依赖外部测试设备的情况下,对芯片的某些部分进行测试,提高了测试的便利性和可靠性。浙江AI芯片工艺